Product Summary

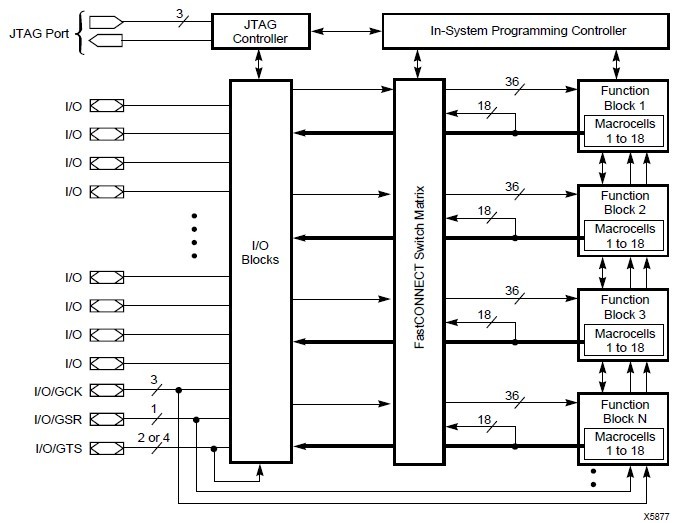

The XC9572-15PQ100C is a in-system programmable CPLD.

Parametrics

Absolute maximum ratings: (1)density range: 36 to 288 macrocells with 800 to 6,400 usable gates; (2)I/O capability: 3.3V or 5V.

Features

Features: (1)High-performance: 5 ns pin-to-pin logic delays on all pins; fCNT to 125 MHz; (2)Large density range: 36 to 288 macrocells with 800 to 6,400 usable gates; (3)5 V in-system programmable: Endurance of 10,000 program/erase cycles; Program/erase over full commercial voltage and temperature range; (4)Enhanced pin-locking architecture; (5)Flexible 36V18 Function Block: 90 product terms drive any or all of 18 macrocells within Function Block; Global and product term clocks, output enables, set and reset signals; (6)Extensive IEEE Std 1149.1 boundary-scan (JTAG) support; (7)Programmable power reduction mode in each macrocell; (8)Slew rate control on individual outputs; (9)User programmable ground pin capability; (10)Extended pattern security features for design protection; (11)High-drive 24 mA outputs; (12)3.3 V or 5 V I/O capability; (13)Advanced CMOS 5V FastFLASH technology; (14)Supports parallel programming of multiple XC9500 devices.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XC9572-15PQ100C |

|

IC CPLD 1.6K 72MCELL 100-PQFP |

Data Sheet |

Negotiable |

|

||||||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||

|

XC9500 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9500XV |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9501 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9502 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9503 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9503B093AR-G |

|

IC REG BUCK ADJ 1A DL 10MSOP |

Data Sheet |

|

|

||||||||||||||||

(China (Mainland))

(China (Mainland))